當(dāng)前位置:

首頁(yè)

>

產(chǎn)品大全

>

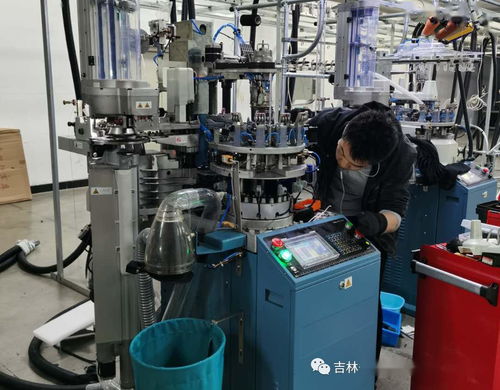

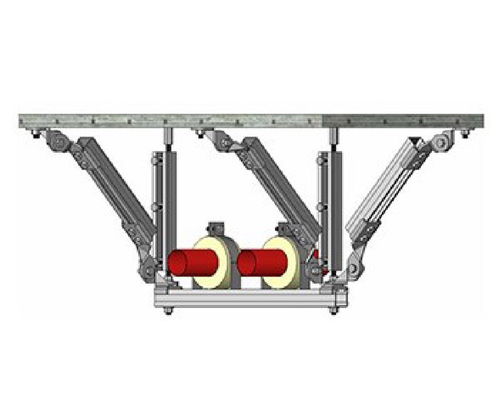

廠家直銷新款印舉重塑膠輪子非標(biāo)移印機(jī)圖片,廠家直銷新款印舉重塑膠輪子非標(biāo)移印機(jī)圖片大全,東莞市力天印刷機(jī)械-

廠家直銷新款印舉重塑膠輪子非標(biāo)移印機(jī)圖片,廠家直銷新款印舉重塑膠輪子非標(biāo)移印機(jī)圖片大全,東莞市力天印刷機(jī)械-

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.citptc.cn/product/62.html

更新時(shí)間:2026-04-17 02:58:47